聚焦支撑40Gbps以上高速信号传输的连接器(以USB Type-C为主)接触性能要求,通过构建连接器三维模型并结合FDTD(有限差分时间域)解析方法,系统探究连接器结构对信号传输质量(SI)和电磁干扰(EMI)的影响,为下一代高速连接器设计提供技术依据。以下从研究背景与目的、核心研究内容、关键结论与价值三方面展开解释:

一、研究背景与目的:为何聚焦“40Gbps级连接器接触性能”随着大数据、高清视频等需求爆发,信息设备信号传输速率从传统USB 2.0(480Mbps)跃升至USB4(40Gbps)、HDMI 2.1等GHz频段标准,高速信号传输对连接器的“接触性能”和“结构兼容性”提出严苛要求,核心痛点与研究目标如下:

1. 高速传输下的核心技术痛点- 结构不连续性导致信号劣化**:连接器(如USB Type-C)需与印刷基板(PCB)对接,PCB采用“准TEM模式”传输的差动线,而连接器存在立体屈曲的线路结构——即便两者特性阻抗理论匹配,电磁场上仍会因“线路结构不连续”产生信号反射、衰减,进而影响SI(信号完整性)和EMI(电磁干扰),但这种关联此前未被量化。

- Type-C连接器设计复杂度高**:相比传统USB Type-A,Type-C形状更复杂、构成要素更多(如4对高速差动线),高周波适配难度大;同时,连接器与线缆的非预期电磁噪声可能导致信息泄露,安全性存隐患。

- **现有研究局限性**:此前研究仅针对USB Type-A的FDTD解析,证实“信号上升速度越快,连接器阻抗变化越大、EMI越强”,但Type-C已成为USB4主流,其40Gbps传输的性能瓶颈亟待破解。

2. 核心研究目标本研究围绕两大核心方向展开,旨在填补高速连接器性能解析的空白:

1. 明确USB Type-C结构对“信号传输劣化”“阻抗变化”的影响,构建含“通用不匹配”的连接器模型,并开发电磁环境劣化预测方法;

2. 针对连接器接触界面的不匹配问题,推定其等效电路网络,量化接触性能对信号传输的影响。

二、核心研究内容:如何通过“模型构建+解析”破解性能瓶颈研究通过“USB规范梳理→三维模型构建→FDTD解析→实验验证”的逻辑链,系统分析Type-C连接器的高速传输特性,核心步骤如下:

1. 基础:USB规范与信号传输原理梳理首先明确各USB版本的速率、连接器类型及技术差异,为后续模型设计提供依据,关键规范对比如下表:

| USB版本 | 最大传输速率 | 连接器类型 | 核心技术特点 | 阻抗要求(差动) |

|-------------|--------------------|-----------------|--------------------|--------------------------|

| USB 1.1 | 12Mbps | Type-A | 基础低速传输 | - |

| USB 2.0 | 480Mbps | Type-A/C | 新增Hi-SPEED模式 | - |

| USB 3.0 | 5Gbps | Type-A/C | 超高速传输,Type-A接口蓝色标识 | 90Ω±20Ω |

| USB 3.1 Gen2 | 10Gbps | Type-A/C | 速率翻倍,兼容前代 | 90Ω±20Ω |

| USB 3.2 Gen2×2 | 20Gbps | Type-C | 2对差动线并行,仅Type-C | 90Ω±20Ω |

|

USB4.0 | 40Gbps | Type-C | 整合USB3.2/Thunderbolt3,支持双向传输(2对差动线上行40Gbps+2对下行40Gbps) | 85Ω±9Ω |

关键原理:USB4的40Gbps传输需满足“5GHz基本频率+24GHz模拟带宽”(因需覆盖高次谐波),解析时需确保40GHz频段的兼容性;速率与频率的关系为“1GHz对应2Gbps”(1周期传输2bit数据),因此5GHz对应10Gbps,4对差动线(TX×2+RX×2)合计实现40Gbps。

2. 核心:USB Type-C三维模型构建为精准模拟连接器与PCB的对接状态,研究创新采用“3DCAD+切片软件+数据压缩”的模型构建方法,步骤如下:

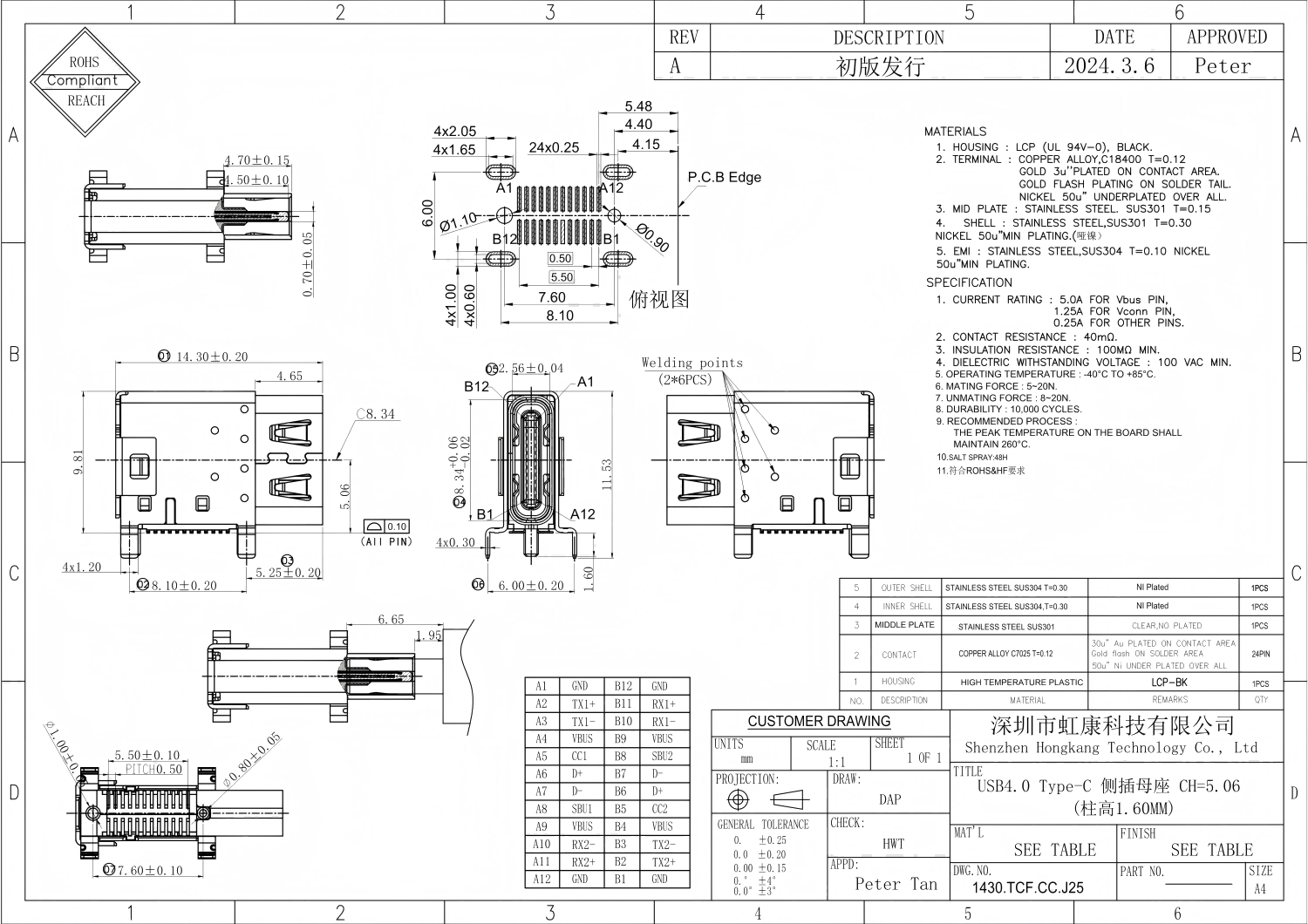

1. 3DCAD建模:用AutoDesk Fusion 360,参考公开USB图纸手动构建Type-C连接器(含外壳、内部 dielectric基板、金属电极),通过“面创建→挤压(交叉/切割/结合)→内部空间生成”的流程,还原立体结构;

2. 切片与格式转换:用3D打印切片软件(Ultimaker Cura)将CAD模型(STL格式)沿高度方向切片,输出含“各层印刷路径”的G-code文件;

3. FDTD适配与数据压缩:用Microsoft Visual C#编写程序,将G-code转换为FDTD解析所需的二进制网格数据;因模型数据量达数百MB(1cell=1byte),采用“连长压缩法(RLE)”压缩(如“AAAAA”→“A5”),利用“自由空间/基板等介质连续分布”的特点,大幅降低数据量,避免解析时内存占用过高。

模型关键参数:Type-C连接器与PCB的对接模型采用FR-4基板(4层,2层为接地层),基板厚度0.8mm,信号层与接地层距离0.06mm;差动线参数为“线宽0.1mm、线间距0.31mm”,确保差动阻抗84.8Ω(接近USB4的85Ω标准)。

3. 核心解析:FDTD(有限差分时间域)法的应用FDTD法是电磁领域主流解析工具,通过“差分离散麦克斯韦方程”,模拟电场与磁场的时间变化,适用于PCB、连接器的EMI/SI分析。本研究的FDTD解析重点关注两大指标:

(1)电界分布解析

向Type-C的差动线(TX±)施加正弦波信号,观察电界在“PCB→连接器→PCB”路径的分布:

- 结果证实:信号可从输入端口(Port1/3)沿x方向传输至输出端口(Port2/4),模型能准确还原实际传输过程;

- 关键发现:连接器内部、连接器与PCB的对接处电界强度显著升高,是电磁辐射(EMI)的主要来源,需重点优化这些区域的结构连续性。

(2)传输特性评价:S参数与TDR解析

通过“S参数(频率域)”和“TDR(时域反射)”双维度,量化信号传输质量与阻抗变化:

- S参数解析(频率域):

- 定义差动传输损耗(Sdd21)、差动反射(Sdd11)等参数,评价信号在不同频率的透反射特性;

- 关键结论:Type-C在25GHz以内的Sdd21(传输损耗)均在-7dB以内,相比Type-A(1.7GHz以上损耗周期性波动),**高周波带宽更宽、反射更小**,更适配40Gbps传输;且Type-C的TX±(位于连接器边缘,靠近金属外壳)比D±(位于中央,对称结构)的共模反射(Scd11)高约20dB,证实“结构位置影响电磁兼容性”。

- TDR解析(时域反射): - 施加不同上升时间(10ps~400ps)的阶跃信号,测量阻抗变化,反映线路结构连续性;

- 关键结论:

1. Type-C的差动阻抗实测86Ω(符合85Ω±9Ω标准),Type-A实测92Ω(符合90Ω±20Ω标准),模型精度达标;

2. PCB与连接器的对接处阻抗变化最大(Type-A尤为明显),源于线路立体屈曲导致的结构不连续;

3. Type-C的插头-插座嵌合处阻抗变化约12Ω,Type-A仅数Ω,说明Type-C的嵌合结构对阻抗匹配要求更严苛。

-

实验验证:接触界面性能的实测分析为验证解析结果,研究通过“TDR实测”和“眼图(Eye-Diagram)尝试”,量化接触界面的不匹配影响:

- TDR实测:

- 搭建实验平台:将Type-C连接器(插头/插座)实装在FR-4基板(90Ω微带线)上,用6ps上升时间的TDR信号(空间分辨率0.646mm)测量阻抗变化;

- 结果:同一品牌的插头-插座对接,阻抗变化≤0.85Ω;不同品牌对接,最大阻抗差达3.75Ω,证实“品牌间结构差异导致接触不匹配,影响信号质量”;且“信号上升速度越快,阻抗变化捕捉越精准”,需用高速TDR评价结构不连续性。

- 眼图尝试:

- 目标:通过眼图直观反映USB4信号的时序抖动、噪声;

- 挑战:现有示波器(8GHz带宽)无法覆盖USB4的24GHz模拟带宽,实测信号(MacBook Air输出0.1Vp-p,惠普输出0.3Vp-p)数据量不足,暂未生成有效眼图,后续需升级25GHz以上示波器。

三、关键结论与研究价值

1. 核心结论1. Type-C的高周波优势明确:相比Type-A,Type-C在25GHz以内传输损耗更小、反射更低,是40Gbps传输的最优选择,但需重点优化“连接器与PCB对接处”“嵌合界面”的结构连续性,降低阻抗突变;

2. 接触界面不匹配影响显著:不同品牌连接器对接时,阻抗差最大达3.75Ω,可能成为信号劣化的瓶颈;连接器边缘的差动线(如TX±)因靠近金属外壳,共模噪声更强,需优化布局;

3. 模型与解析方法有效:基于“3DCAD+FDTD+RLE压缩”的模型能精准还原Type-C的电磁特性,TDR解析可量化阻抗变化,为连接器设计提供可复用的解析工具。

2. 研究价值与未来方向

- 实用价值:提供了一套“从模型构建到性能预测”的高速连接器解析流程,可直接指导USB4、HDMI 2.1等连接器的设计,降低SI/EMI风险;

- **未来计划**:

1. 引入X射线CT设备,自动获取连接器内部结构数据,替代手动建模,缩短研究周期;

2. 升级25GHz以上示波器,生成USB4信号的眼图,更直观评价时序性能;

3. 结合激光显微镜观察连接器表面劣化(如插拔导致的微划痕),分析接触电阻与信号质量的关联。

总结本研究通过“模型构建-解析-实验”的闭环,首次系统量化了USB Type-C连接器在40Gbps传输下的性能瓶颈:**结构不连续性(对接处、嵌合界面)和接触不匹配(品牌差异)是影响SI/EMI的核心因素**,同时提供了可复用的解析工具与设计优化方向,为下一代高速连接器的研发奠定了关键技术基础。